Executive Certification in VLSI Design for Testing

About the Course:

In the AI era, chip designers are empowered with AI-powered EDA tools, silicon-proven IP libraries, and open computing platforms like RISC-V, enabling the efficient design of powerful SoCs for next-generation products. However, ensuring testability and fault coverage is equally critical for first-pass silicon success. This is the right time for chip designers and VLSI enthusiasts to explore ASIC Design for Testing (DFT) methodologies—covering scan insertion, ATPG, fault modeling, BIST, boundary scan, JTAG, and advanced techniques for low-power and high-performance designs. A strong foundation in DFT ensures high-quality, reliable SoCs ready for mass production.

This course provides a comprehensive foundation in Design For Testing. Learners begin with an overview of VLSI, Moore’s Law, SoC architecture, and design flows, followed by digital logic fundamentals such as number systems, combinational and sequential circuits, FSMs, and memory design. The course advances into practical hardware design and verification using Verilog HDL programming - coding styles, FSM design, and lab exercises. It then walks you through CMOS fundamentals, Synthesis, Clock Domain Crossing, STA, Equivalence Checking, and Physical Design Flow - floor planning, placement, CTS, routing, layout compaction, and physical verification (DRC, LVS, IR drop, EM), with labs and case studies.

The Design For Testing module covers verification vs testing, scan insertion, ATPG, fault modelling, BIST, boundary Scan, Test compression, DRC & Test coverage, JTAG, DFT for Analog Macros, while automation skills are developed with Tcl and Python scripting. Students also learn version control with Git, before progressing to advanced DFT concepts and doing an industry standard project – DFT implementation on an SoC.

Our Students Rate This Course

Trainer

Program Fee

Rs 2,00,000 + GST

Available Seats

100

Schedule

9 Months

Only Few Seats Left

Reviews

Testimonials

NEWS & UPDATES

Career Transitions

55% Average Salary Hike

$1,27,000 Highest Salary

800+ Career Transitions

300+ Hiring Partners

Who Can Apply for the Course?

- Anyone with a bachelor’s degree and a passion for VLSI

- Professionals looking to grow their career in VLSI

- Any IT Professional with a bachelor’s degree looking to transition into VLSI design and semiconductor technologies

- Project/Product Managers aiming to transition into or deepen their understanding of VLSI and chip design

- Engineers who aspire to use industry-standard EDA tools and build their own chips from concept to layout

About Program

At iHUB DivyaSampark, we are driven by the belief that young, innovative minds have immense potential to transform the world. Our core mission is to develop highly knowledgeable human resources with top-order, industry-relevant skills.

Whether you are looking for a career transition, a significant salary hike, or to master specialized knowledge, our programs provide the mentorship and practical exposure needed to achieve successful career outcomes and help you secure roles with our network of 300+ hiring partners

Key Highlights

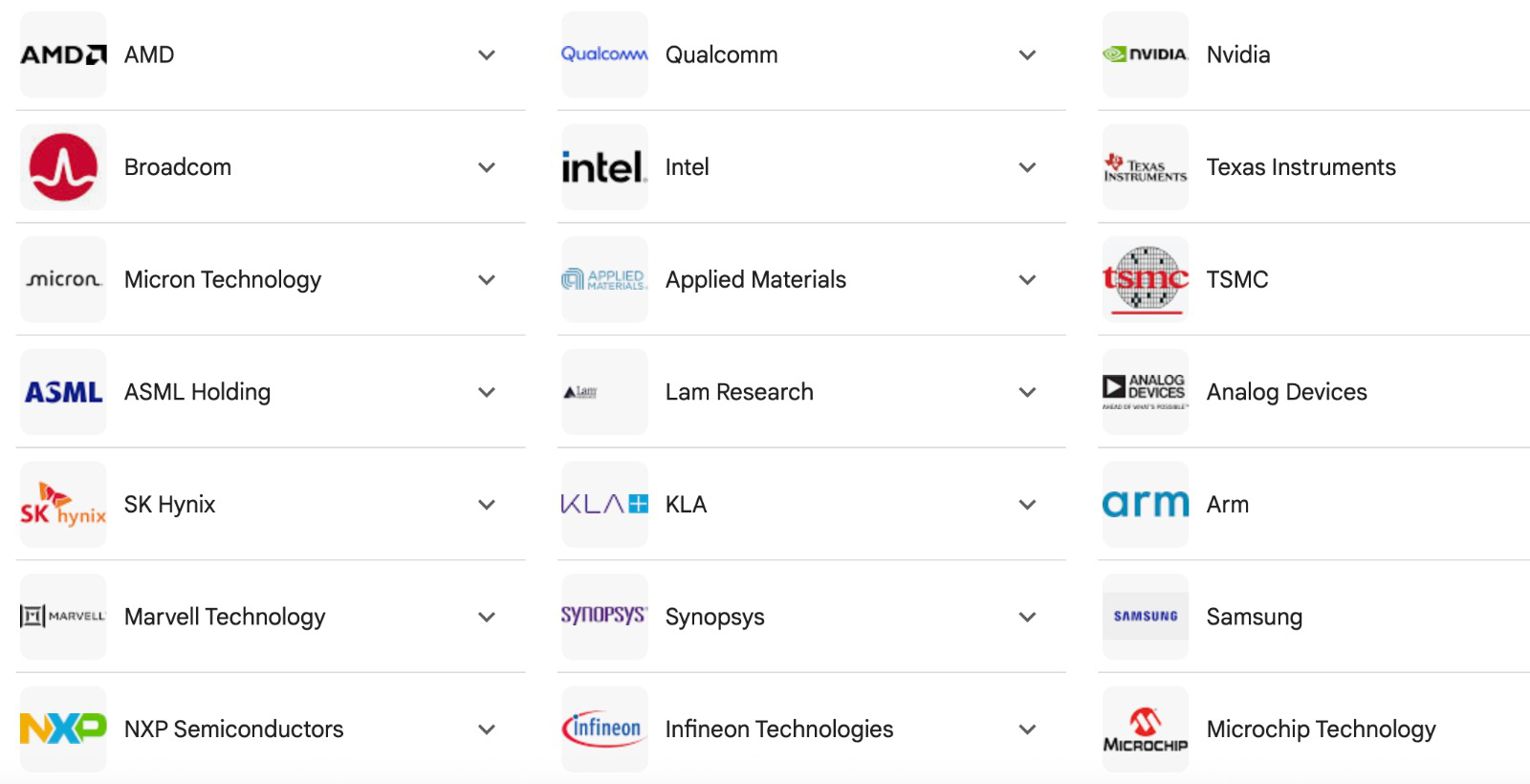

Our Alumni Work At

What is included in this course?

- Non-biased career guidance

- Counselling based on your skills and preference

- No repetitive calls, only as per convenience

- Rigorous curriculum designed by industry experts

- Complete this program while you work

I’m Interested in This Program

Courses

Other Courses You Might Be Interested In

Certificate

Rs. 65,000 + GST/-

Advanced Certification in Data Science and AI

Learn Data Science and AI from IIT Faculty with Campus Immersion @ IIT Roorkee

Certificate

Rs. ₹60,000 + GST*/-

Future-Ready Product Management with Applied AI Program

6 Months | 4-5 hours per week

MASAI

MASAI

Certificate

Rs. 2,00,000 + GST/-

Executive Post Graduate Certification in VLSI SoC Design and Verification

12 Months

MAVEN silicon

MAVEN silicon